AMD EPYC Venice「Zen 6」ESが3つのSP7プラットフォームから流出

AMDの次世代サーバーCPU、EPYC Venice「Zen 6」のエンジニアリングサンプルがベンチマークデータベースに姿を現した。まだ誰も触れていないはずのチップが、すでに静かに動き始めている。

AMDの次世代サーバーCPU、EPYC Venice「Zen 6」のエンジニアリングサンプルがベンチマークデータベースに姿を現した。まだ誰も触れていないはずのチップが、すでに静かに動き始めている。

「コンゴ」「ケニア」「ナイジェリア」──アフリカの名を冠した評価基板

AMDが顧客向けに出荷を始めたVeniceのエンジニアリングサンプル(ES)が、OpenBenchmarkingデータベースに複数登録されている。

注目すべきは、今回確認されたSP7プラットフォームの評価基板(EVB)に付けられた名前だ。Congo、Kenya、Nigeria──いずれもアフリカの国名がコードネームとして採用されている。AMDのEPYCファミリーはイタリアの都市名(Milan、Genoa、Turin、Veniceなど)をCPUに使うが、プラットフォーム側にアフリカの国名を振るのは興味深い。

それぞれの基板には異なる構成のVenice ESが搭載され、1ソケットと2ソケットの両環境でテストが進行中だ。

Venice(コードネーム)は、現行のEPYC 9005「Turin」(Zen 5)の後継にあたる第6世代EPYCで、TSMCの2nmプロセスで製造される初のサーバーCPUだ。最大256コア/512スレッドに対応し、2026年後半の投入が見込まれている。

6種のESサンプルが示すダイ構成

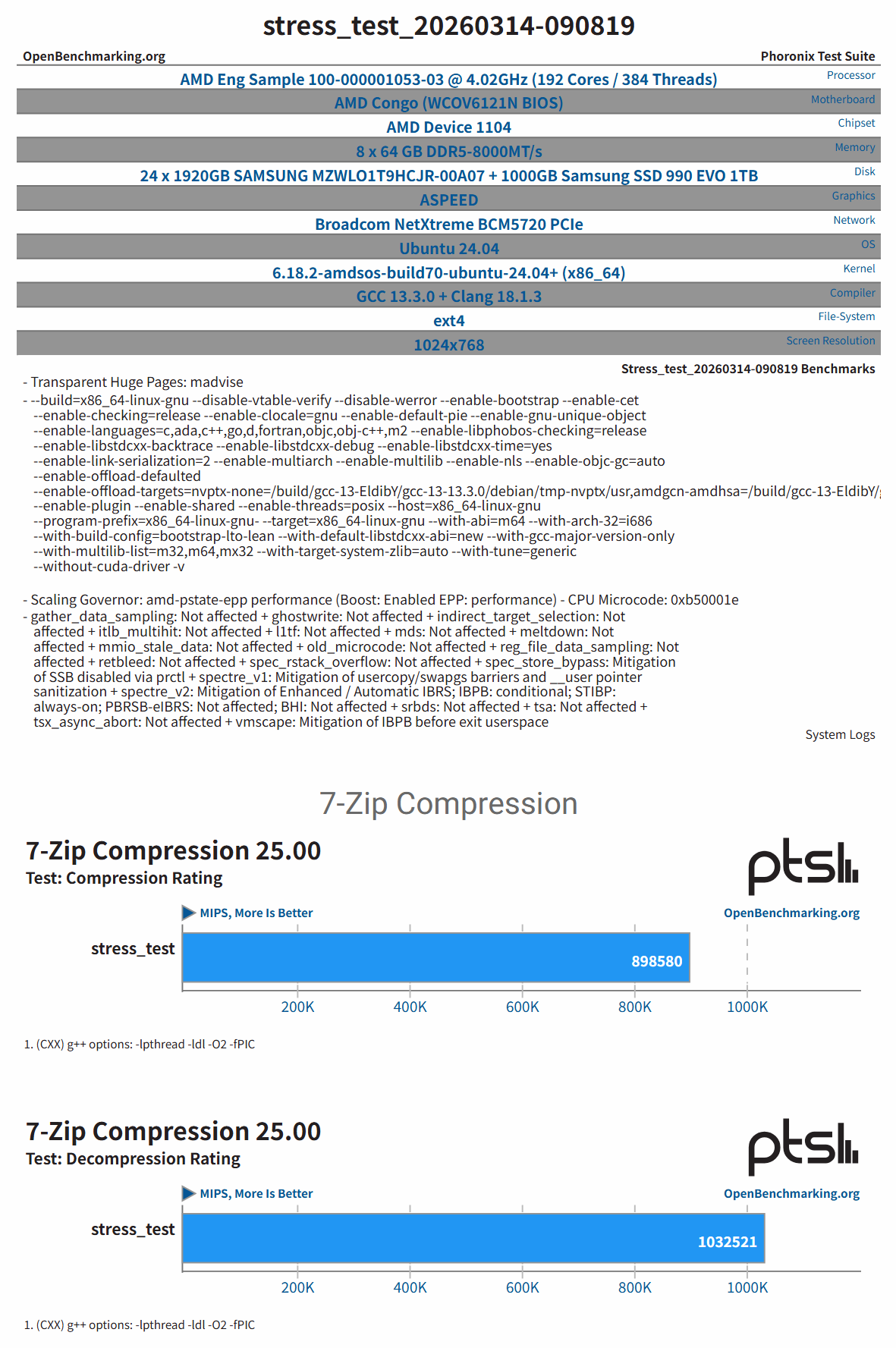

合計6種類のVenice ESがOpenBenchmarkingに登録されている。ダイ構成はそれぞれ異なり、AMDがSP7プラットフォーム上で幅広い検証を進めていることがうかがえる。

100-000001053-03 192C/384T 8CCD + 2IOD

100-000001051-08 192C/384T 2x(8CCD + 2IOD)

100-000001056-09 128C/256T 4CCD + 2IOD

100-000001056-03 128C/256T 2x 4CCD + 2IOD

100-000001863-02 64C/128T 2CCD + 2IOD

100-000002138-02 64C/128T 2x 2CCD + 2IOD

最上位のサンプルは192コア/384スレッド仕様で、8基のCCDと2基のIOD(I/Oダイ)で構成される。1CCDあたり24コアという計算になり、これはZen 6C(高密度版)のCCDが最大32コアであることから、一部コアが無効化されたES段階であることを示している。動作クロックは4.02GHz、メモリはDDR5-8000MT/sの64GBモジュールを8枚搭載していた。

128コア/256スレッドのサンプルは4CCD+2IOD構成で、1CCDあたり32コア──Zen 6CのCCDがフル稼働している。64コア/128スレッドのサンプルも2CCD+2IOD構成で32コア/CCDだ。

2Pプラットフォーム「Nigeria」では、64GB DDR5-8000MT/sモジュールを32枚搭載し、合計2TBという圧倒的なメモリ容量での動作が確認されている。サーバー1台でこれだけのメモリを扱えるというのは、仮想化やインメモリデータベースの運用者にとって無視できない数字だ。

未完成のチップが、すでに現行世代に迫る

ベンチマーク結果はESの段階であることを差し引いても、意外なほど力強い。

Congoプラットフォーム上の192コアサンプルは、7-Zip圧縮テストで約89万8,580 MIPS、展開テストでは約103万MIPS超を記録した。現行EPYC Turin(1P・192コア)と比較すると、圧縮ではTurinの約101万MIPSにわずかに及ばないが、展開ではTurinの約81万MIPSを27%上回った。

エンジニアリングサンプルはクロックやファームウェアが最適化されていない初期段階のチップであり、最終製品とは性能が大きく異なる可能性がある。今回のスコアは参考値として見るべきだ。

Kenyaプラットフォーム上の128コアサンプルのx265エンコード結果も目を引く。Bosphorus 4Kテストで46.55fpsを記録し、現行Turin 128コアの約35.3fpsを約32%上回った。同じコア数でこの差が出ているということは、Zen 6アーキテクチャ自体のIPC改善が寄与している可能性が高い。

64コアサンプルは興味深い位置づけだ。動作クロックが3.52GHzと192コア版より低く、メモリもDDR5-6400MT/sに抑えられており、7-Zip圧縮は約44万6,000 MIPSでTurin 64コアの約48万9,000 MIPSをやや下回る。ESの初期段階でクロックもメモリも控えめな構成であることを考えれば、伸びしろは十分に残されている。

ただし、このクラスのベンチマークではメモリ構成の違いがスコアに直結する。Venice ESがDDR5-6400MT/sを4枚使っていたのに対し、比較対象のTurinがどのメモリ構成だったかで解釈は変わる。数字の「大きさ」だけで判断するのは早計だ。

SP7プラットフォームの全体像

今回の流出は、SP7プラットフォームの実像を具体的に示してもいる。

Congoは1P、Nigeriaは2P、Kenyaも1Pとして動作していた。すべてのテストで「AMD Device 1104」というチップセット情報が共通しており、SP7プラットフォームの統一的な設計思想が見て取れる。

AMDは以前から、SP7で最大16チャネルのDDR5メモリ、PCIe Gen 6.0を128レーン、ソケットあたり1.6TB/sのメモリ帯域を実現すると表明している。現行SP5の614GB/sから2.6倍という飛躍だ。TDPも最大600Wまで引き上げられる見込みで、従来の空冷では限界に達する領域に踏み込む。

HPEはすでにSP7対応のスーパーコンピュータノード「GX5000」を公開しており、プラットフォーム側のエコシステムも着実に動いている。

ESの流出が意味するもの

Veniceの開発は予定通り進んでいる。AMDのリサ・スーCEOは2025年6月のAdvancing AIイベントで「ラボに戻ってきたばかりで、非常に良い仕上がりだ」と述べ、CES 2026ではSP7上の実物シリコンが初公開された。

今回のES流出は、こうしたロードマップが着実に実行されていることの傍証だ。OpenBenchmarkingへの登録日は2026年1月から3月にかけて散在しており、バリデーションが継続的に進んでいることがわかる。

AMDが公約する70%の性能向上(SPECrate 2017 INT基準)を実現するには、コア数の33%増に加え、IPC改善とクロック向上が不可欠になる。

TSMCの2nm(N2P)プロセスはFinFETからナノシート(GAA)トランジスタへの世代交代であり、同電力で10〜15%の性能向上が見込まれている。AMDにとって、プロセス技術の恩恵とアーキテクチャ改善の両輪がどこまで噛み合うかが勝負だ。

正直なところ、ESの段階でここまでのスコアが出ているのは心強い。ただし、AMDのマーケティング数値と実環境での性能には常にギャップがある。楽観も悲観も、最終シリコンが出揃うまで保留しておくのが賢明だろう。

半年後にVeniceの製品版が登場したとき、今日のベンチマークがどれほど控えめだったかを笑って振り返れるだろうか。

参照元

#AMD #EPYC #Venice #Zen6 #SP7 #サーバーCPU #データセンター #TSMC #2nm #DDR5 #PCIeGen6 #ベンチマーク #CPU