Intel 8086の「遅すぎる掛け算」を2.5倍速にしたISAカードの話

2026年に、1980年代のチップで「掛け算が遅い」という40年越しの問題を力技で解決した人がいる。しかも、自作のISA拡張カードで。

2026年に、1980年代のチップで「掛け算が遅い」という40年越しの問題を力技で解決した人がいる。しかも、自作のISA拡張カードで。

8086は掛け算が致命的に遅かった

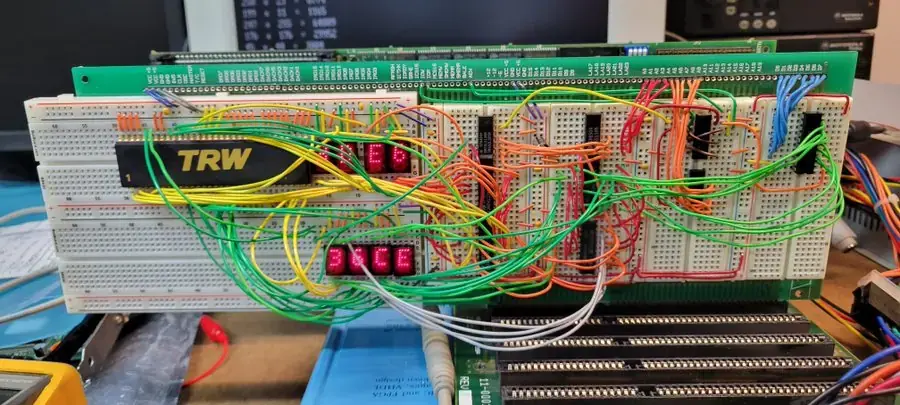

コンピュータサイエンティストのブラッド(@bradthx)が、Intel 8086/8088向けのハードウェア乗算アクセラレータカードを自作し、Xで公開した。

https://x.com/bradthx/status/2039703302695182551

なぜわざわざそんなものを作るのか。理由は単純だ。初期のx86プロセッサにおけるMUL命令は、率直に言って使い物にならないほど遅い。整数乗算が約2.5倍高速化されるというこのカードの成果が、その「遅さ」の深刻さを物語っている。

8086のMUL命令は、マイクロコードで制御されるシフト&加算の繰り返しで実装されていた。ブラッドの言い方を借りれば、「紙の上でやる筆算のバイナリ版」をCPU内部でひたすら回していたのだ。

8ビットレジスタ同士の乗算で70〜77クロックサイクル、16ビットなら118〜133サイクルかかる。5MHzの8086では、たかが1回の掛け算に14〜15マイクロ秒を浪費する計算だ。

ADD命令がわずか3サイクルで済むことを考えると、この遅さは異常だ。1982年に登場した80286がMUL命令を21サイクルにまで短縮したのは、Intel自身がこのボトルネックをわかっていた証拠だろう。

40年前の軍用チップを引っ張り出す

ブラッドが目をつけたのはTRW社のMPY12HJだ。12×12ビットの並列乗算器で、もともと航空宇宙や軍事用途の高速信号処理向けに設計されたチップである。

このチップが面白いのは、完全に非同期で動作するところだ。クロック信号がいらない。ビットがシリコン内部を伝播する速度がそのまま演算速度になる。CPUがマイクロコードをぐるぐる回している間に、こいつは一瞬で答えを出す。

TRW LSI Productsは、TTLロジックゲートの発明者ジェームズ・ビューイが在籍した半導体部門だ。航空宇宙・ミサイル誘導のDSP需要を背景に、1976年から並列乗算器の開発を進めていた。MPY12HJはその系譜に連なるチップで、ソ連もM1802VR4としてクローンを製造したほど実績がある。

TRW乗算器シリーズは1970年代後半から1980年代に生産されていた。つまり、1981年にIBM PCがISAスロットを世に送り出した時点で、このアプローチは技術的に実現可能だった。当時のエンジニアが「MUL命令が遅いなら外部ハードウェアで殴ればいい」と思わなかったとは考えにくい。コストと需要のバランスが合わなかったのか、それとも単に誰もやらなかっただけなのか。

ISAバスのボトルネックをどう潰したか

ISAカード上に乗算器を置くということは、CPUとカードの間でデータをやり取りするバス転送のオーバーヘッドが発生する。

バス転送の中身

初期ISAバスは8ビット幅しかない。1回の乗算では、オペランドAとBの書き込み2回、結果の上位・下位バイト読み出し2回、計4回のバス転送が必要になる。

ブラッドの計算によれば、この一連の転送にかかるコストは32CPUクロック、5MHzでの時間換算で約6.4マイクロ秒だ。

ここでTRW乗算器の非同期性が効いてくる。115ナノ秒で乗算結果が確定するということは、バスがデータを運んでいる間に、チップはとっくに答えを出し終わっている。乗算器自体の計算時間は事実上ゼロに近く、実効的なボトルネックはバス転送のみだ。

CPUの内蔵MUL命令が14〜15マイクロ秒かかるのに対し、このカードは約6マイクロ秒で処理を完了する。差し引き約8マイクロ秒の短縮で、トータル約2.5倍の高速化。遅い掛け算を力技で殴り倒した格好だ。

既存ソフトは速くならない

ここが一番大事な点だ。このカードは、既存のコンパイル済みアプリケーションを勝手に高速化するものではない。

CPUのMUL命令をハードウェアレベルで横取りする仕組みではなく、専用サブルーチンを経由して呼び出す設計だ。ブラッドはXで「自分が書くプログラムでは、内蔵のx86 MUL命令の代わりにハードウェア乗算器を使う独自サブルーチンを呼べる」と説明している。だから、手元にあるDOSゲームやビジネスソフトがいきなり速くなることはない。

ブラッド自身、「2026年に必要なものではないのは明白だ。けど、作る価値は間違いなくあった」と言い切っている。

この制約は、1980年代に実在した286アクセラレータカード(Intel InBoard 386など)とは対照的だ。それらはCPUソケットにリボンケーブルで接続し、既存ソフトを透過的に高速化できた。乗算「だけ」を外部ハードウェアに投げるという発想が当時製品化されなかったのは、この互換性の壁が大きかったのだろう。

同じ発想は今も繰り返されている

汎用プロセッサの内部で汎用的に処理するか、専用ハードウェアにオフロードするか。この判断は、2026年の今もまったく同じ形で存在している。

40年前の乗算器と現代のAMX

Intel自身が2023年にSapphire Rapidsで導入したAMX(Advanced Matrix Extensions)は、行列演算を専用ハードウェアにオフロードする仕組みだ。GPUやNPUも本質的には同じアプローチで、「CPUが苦手な処理は専用ハードウェアに任せろ」という設計判断にほかならない。

ブラッドのカードがやったことは、スケールこそ違えど構造は同じだ。遅い処理を見つけて、専用チップに丸投げする。半導体業界が半世紀かけてたどり着いた結論を、1枚のISAカードとヴィンテージチップで実演してみせた。

「2026年に必要ない」とブラッドは言うが、この設計思想は2026年のデータセンターでも主役を張っている。変わったのはトランジスタの数であって、考え方ではない。

参照元

関連記事

- Linux 7.1、37年間続いたi486サポートに幕を下ろす

- Nova LakeはIPC優位、クロックはZen 6が制す

- Nova Lake-Sの42コアが44コアに増量、Intelが設計を修正

- Core Ultra 7 270K Plus即完売、歪んだ国内初値

- Intel封印の12Pコア、市販マザボでWindows起動に成功

- IntelのArrow Lake Refreshが評価された矢先に、年間30%の値上げ計画が浮上している

- Nova Lake-HXのコア構成が流出——28コアの強さと、2コアiGPUという割り切り

- Intel「Wildcat Lake」全6モデルの仕様が流出──格安PCの景色が変わる

- Intel BOTの命令変換、Geekbenchが解析

- Intel Arrow Lake Refresh、発売2日で希望小売価格を超える値付けが全米で常態化