Nova Lake-Sの42コアが44コアに増量、Intelが設計を修正

あの「7コア」の違和感が、ようやく解消される。Intelの次世代デスクトップCPU「Nova Lake-S」で、デュアルコンピュートタイル構成の下位SKUが42コアから44コアにスペックアップした。

あの「7コア」の違和感が、ようやく解消される。Intelの次世代デスクトップCPU「Nova Lake-S」で、デュアルコンピュートタイル構成の下位SKUが42コアから44コアにスペックアップした。

コンピュートタイルの対称性を取り戻す

Nova Lake-Sのコア構成に変更が入った。リーカーのJaykihnが4月4日に投稿した情報によれば、デュアルコンピュートタイル構成の下位モデルが42コアから44コアに引き上げられている。

https://x.com/jaykihn0/status/2040172580200443914

変更の核心は「タイルあたりのP-Core数」にある。従来の42コア構成は14P+24E+4LPEで、これは各タイルに7基ずつP-Coreを振り分ける計算だった。だが、Nova Lake-Sのコンピュートタイルは本来8P+16Eまたは8P+12Eの構成を基本設計としている。タイルあたり7基というのは、8基のうち1基を無効化した「半端な選別品」を意味する。

新しい44コア構成は2×(8P+12E)+4LPE。つまり、両方のタイルでP-Coreがフル8基有効になる。変更前の42コアから44コアへの引き上げは、たった2コアの差に見えて、設計思想の転換を意味している。「2x(8+12)+4に置き換えられた認識で合っているか」というフォロワーの質問に、Jaykihnは端的に「Yes」と返答した。

これまでの42コア構成(14P+24E+4LPE)は各タイルに7基のP-Coreを配分していた。Nova Lake-Sのタイル設計は8P単位が基本であるため、7基は設計上の不整合だった。今回の修正で対称性が確保される。

この変更は「2コアの純増」と読むより、設計の不合理を正したと読むべきだろう。タイルあたり7Pという構成は、歩留まりの観点では柔軟だが、ソフトウェアスケジューリングの対称性を損なう。特にNova Lake-SはbLLC(Big Last-Level Cache)を両タイルに搭載する設計を採用しており、キャッシュアクセスの対称性がアーキテクチャの売りだ。

コア構成まで対称にすることで、その思想が一貫する。

最上位52コアとの棲み分けが鮮明に

52コアのフラッグシップ構成(2×(8P+16E)+4LPE)に変更はない。つまりNova Lake-Sのデュアルタイルラインナップは、52コアと44コアの2本立てとなる。

注目すべきは、この2モデル間の差がE-Coreの数だけで決まる点だ。P-Coreは両方とも16基(タイルあたり8基×2)。マルチスレッド性能に差がつくのはE-Coreの32基対24基の部分で、ゲーミングのようなP-Core依存のワークロードでは両者の差は縮まる可能性がある。

価格次第では、44コアモデルがゲーマー向けのHEDT入門として面白いポジションを占めるかもしれない。52コアモデルは1,200ドル(約19万2,000円)以上との予測もあり、フルロード時の消費電力は700Wを超えるとされている。44コアなら、電力設計のハードルも幾分低くなる。

Nova Lake-Sのデュアルタイル構成は、Arrow Lake-Sのフラッグシップ「Core Ultra 9 285K」の24コアから一気に倍以上のコア数を実現する。PL1は150W前後と従来並みだが、PL2は約500W、PL4は854Wに達する見込みだ。

非K-SKUにもbLLCが広がる可能性

今回のリーク情報にはもうひとつ重要な示唆が含まれている。Jaykihnは同日の別の投稿で、旧42コアSKUの6+12タイル構成を活用したロック版bLLC SKUが存在する可能性に言及した。

https://x.com/jaykihn0/status/2040172610688868383

「旧42CのSKU向けに、6+12タイルを使ったロック版bLLC SKUが存在するかもしれない」という趣旨で、さらに「Kシリーズの上位にbLLC向けの新セグメントがある」とも述べている。

これまでbLLCはアンロック(K)モデル限定とされてきた。もしロック版にまでbLLCが拡大されるなら、Nova Lake-Sの競争力は一段階上がる。AMDの3D V-Cacheが事実上ゲーミング最強の座を独占してきた状況に、Intelが本腰を入れて挑む構えが見えてくる。

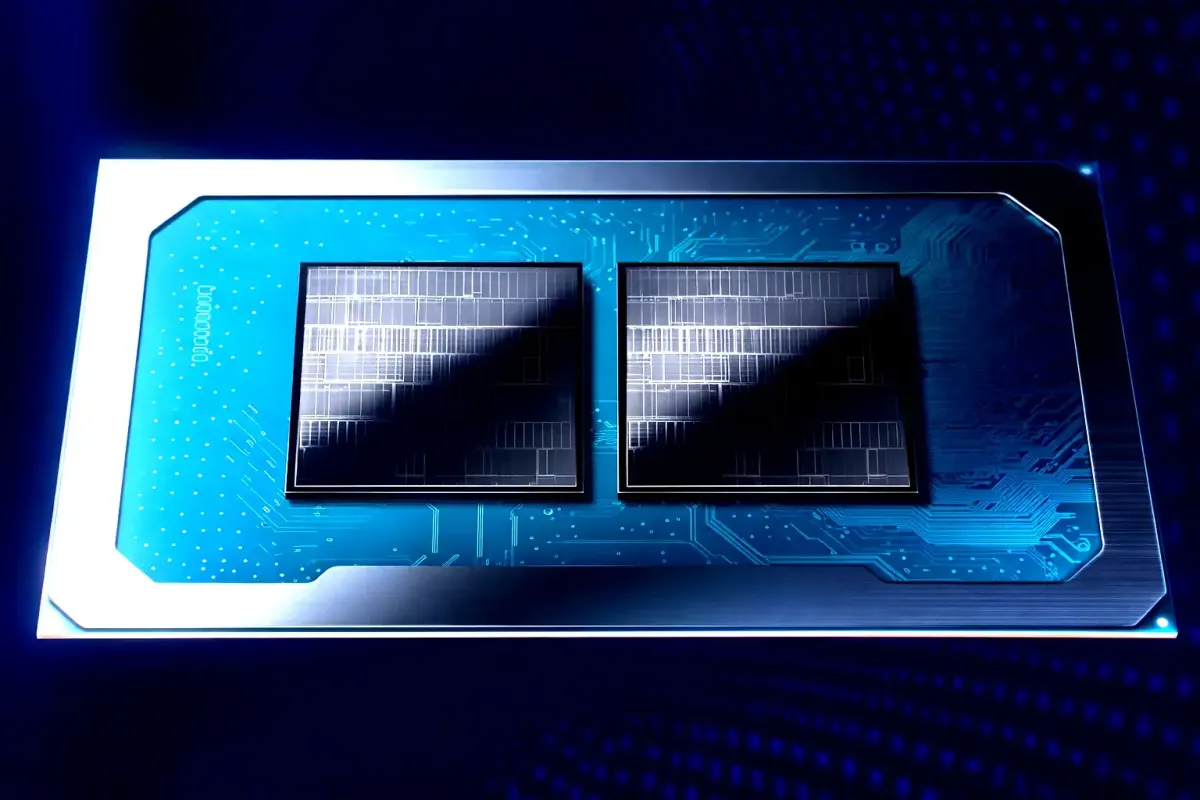

ダイの構造について問われたJaykihnは「シングルダイ。デュアルコンピュートタイルには2つの別々のダイを使う」と回答しており、AMDのCCD方式と同様にモジュラー設計であることが改めて確認された。これまでのK限定路線からbLLCの裾野を広げる方向転換は、AMDの3D V-Cache戦略に対する明確な意思表示だ。

Zen 6との直接対決が見えてきた

Nova Lake-Sの対岸にはAMDのZen 6が控えている。Zen 6はCCDあたり最大12コアへの拡張が見込まれ、デュアルCCDなら24コア+192MBの3D V-Cacheという構成が予想されている。

対するIntel側は、シングルタイルでも8P+16E+144MBのbLLCを擁する28コア構成で対抗。デュアルタイルの44コア・52コアモデルはHEDTセグメントを新たに開拓する。LGA 1954ソケットと900シリーズチップセットによる新プラットフォームへの移行も含め、2026年後半のCPU市場は久しぶりの激戦区になりそうだ。

ただし、すべては暫定情報であることを忘れてはならない。Jaykihn自身が繰り返し「Preliminary」と前置きしているように、Intelがスペックを確定させるまでは数字が動く余地がある。42が44になったように。

参照元

関連記事

- Nova Lake-HXのコア構成が流出——28コアの強さと、2コアiGPUという割り切り

- Core Ultra 7 270K Plus即完売、歪んだ国内初値

- Intel封印の12Pコア、市販マザボでWindows起動に成功

- AMD初の200W CPU、空冷では「性能を取りこぼす」とEKが警告

- Zen 6 PQOS拡張:AMDが帯域幅制御と特権分離を進化させた

- IntelのArrow Lake Refreshが評価された矢先に、年間30%の値上げ計画が浮上している

- Intel「Wildcat Lake」全6モデルの仕様が流出──格安PCの景色が変わる

- Intel BOTの命令変換、Geekbenchが解析

- ASRock製マザーボード1枚がRyzen 7 9800X3Dを3本破壊──BIOS更新は解決策になっていないのか

- Intel Arrow Lake Refresh、発売2日で希望小売価格を超える値付けが全米で常態化