Intel Nova Lake、bLLC最大288MBで9950X3D2超え

Intel次世代「Nova Lake-S」のbLLCキャッシュ構成が5段階で出揃った。最上位288MBで、22日発売のAMD Ryzen 9 9950X3D2を38%上回る。ただ本当の動きは一段下で進んでいる。

5段階のキャッシュ構成が一気に出揃った

リーカーのJaykihn(@jaykihn0)がX上で、Nova Lake-SのbLLC搭載SKUについて5段階の具体的な容量を明らかにした。コア構成と総キャッシュ容量の対応関係は、16+32で288MB、16+24で264MB、8+16で144MB、8+12で132MB、6+12で108MBとなっている。

ここでの数字は各SKUの最大L3キャッシュを示している。2基のコンピュートタイルを積む最上位構成(16+32)では288MB、単一タイルでも最大144MBに達する。最上位の288MBは、9950X3D2の208MBを単純計算で38%上回る容量だ。

| 項目 | 16+32 | 16+24 | 8+16 | 8+12 | 6+12 |

|---|---|---|---|---|---|

| コア構成 | 2タイル | 2タイル | 1タイル | 1タイル | 1タイル |

| 最大bLLC | 288MB | 264MB | 144MB | 132MB | 108MB |

| 想定グレード | Core Ultra X | Core Ultra X | Core Ultra 9 | Core Ultra 7 | Core Ultra 5相当 |

| K/ロック | K | K | K | K | ロック版候補 |

ただ、この勝ち負け自体はそれほど驚く話ではない。bLLCは3D V-Cacheと違ってコンピュートタイルの平面上に直接実装される構造で、ダイサイズで容量を稼ぎやすい。AMDは垂直スタックで省面積を取ったが、Intelは面積を使ってでも総容量を押し上げる方向に振った。容量単体で比較するなら、Intelが勝つのは設計段階でほぼ見えていた。

本当の注目点は「6+12タイル」の扱い

この投稿で目を引くのは、最下位の「6+12で108MB」の行だ。

これまでの報道では、bLLCはK型番(倍率ロック解除)の上位SKUに限定される見込みだった。ところがJaykihnは4月3日の別の投稿で、Core Ultra 7の上位として存在していた「42コア版」が「44コア版」に格上げされたと明らかにしている。この変更で6P+12Eのタイルが宙に浮いた状態になり、それを消化する先として非Kのbllc搭載SKU、つまりCore Ultra 5相当のロック版まで降りてくる可能性が出てきた。Jaykihn本人も同日のXでこう書いている。

暫定情報として。以前の42コアSKUに使っていた6+12タイルを受ける形で、ロック版のbLLC SKUが出てくる可能性がある。(Jaykihn)

これが実現すれば、AMDが7800X3Dや9800X3Dで築いてきた「ゲーマー向けキャッシュモデル」という領域に、Intelが下の価格帯から食い込むことになる。従来のIntelのゲーミング戦略は、K型番にすべてを集約して高価格帯で戦う形だった。その枠を崩して、倍率固定の中価格帯にもキャッシュモデルを投入する動きは、戦略的には大きな転換と言っていい。

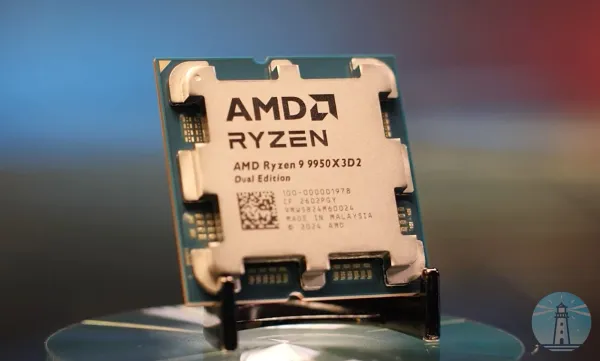

AMDの応戦カードは「Dual Edition」

Intelの動きに対して、AMDは4月22日発売のRyzen 9 9950X3D2 Dual Editionで既に次のカードを切っている。16コア32スレッド、ブースト5.6GHz、TDPは200Wで、L3が192MBにL2が16MB、合わせて208MBの大容量キャッシュを積む。既存のX3Dと違い、両方のCCDに3D V-Cacheを積んだ構成だ。

AMDはこのCPUをゲーマー向けではなく、ワークステーション寄りに位置付けている。レンダリング・コンテンツ制作・AI・ソフトウェアコンパイルなどで、従来の9950X3D比5〜10%の向上を謳う内容だ。MSRPは899ドル(約14万2000円)で、Threadripperの下を埋める価格帯に設定された。

対するNova Lake-Sの52コア版は、TDP 175W、ソケットLGA 1954で2026年後半の投入予定だ。コア数は16対52、スペックシート上の見栄えは大差が付く。ただし、bLLCを搭載した52コア版は製造コストが極めて高くなる見通しで、店頭に並ぶ価格がAMDのDual Editionを大きく上回る可能性は十分にある。

容量だけでは勝負が決まらない理由

ここで一つ冷静になりたいのは、キャッシュ容量が大きければゲーミング性能が自動的に上がるわけではないという点だ。

3D V-Cacheが圧倒的なゲーミング性能を叩き出している理由は、容量そのものよりレイテンシとヒット率の両立にある。垂直スタックで物理的にコア直下に置くことで、大容量と短レイテンシが同居する設計になった。IntelのbLLCはコンピュートタイル上の平面配置なので、容量で勝っても物理距離が遠くなる可能性があり、単純な「MB数」の比較は実性能を保証しない。

ダイスタック構造を使わないため、より多くのキャッシュを載せてもレイテンシはX3Dより不利になる可能性がある。最終的な性能は、コアアーキテクチャ(Coyote Cove / Arctic Wolf)と組み合わせた総合評価で見るしかない。

一方で、AMDの9950X3D2も「208MBの大容量がゲームで決定打になるか」は未知数だ。AMD自身、発表のアピールポイントは生産性ワークロード中心で、ゲーミングベンチは伏せている。過去のX3Dは片側CCDにしかキャッシュを積まない「非対称」設計で、OSのスケジューリングが鍵を握っていた。両CCDに積んだ新設計が、対称構造でむしろ混乱するシナリオもあり得る。

2026年後半に待つ比較の本番

Nova Lake-Sの登場は2026年後半、おそらくCES 2027周辺のタイミングになる。9950X3D2が4月22日に出て、その頃にはZen 6ベースの次世代X3Dも視界に入ってくる。

Intelにとっての本当のハードルは、288MBという数字を持ち出すことではない。108MB版の市場定着こそが鍵になる。Core Ultra 5相当まで下ろしたbLLCを、価格的にも性能的にも納得できる水準で店頭に並べられるか。高価格帯だけなら、ベンチマークで勝てば話は早い。だが中価格帯は、価格とゲーム実性能の両方で納得感が出ないと売れない領域だ。

AMDがX3Dで築いた「ゲーマーに刺さる価格帯のキャッシュCPU」というポジションに、Intelがどう入っていくのか。この一年半のCPU戦線は、コア数よりキャッシュの設計で勝負が決まる流れになりそうだ。

参照元

- Jaykihn(@jaykihn0)- X

- Jaykihn - X投稿(ロック版bLLC SKUに関する言及、4月3日)

- AMD - Ryzen 9 9950X3D2 Dual Edition 製品ページ

関連記事

- Ryzen 9 9950X3D2、予約価格が999ドルに

- Ryzen 9 9950X3D2が中国で先行予約——最大63%高速な$899の全コアV-Cache

- Intel Nova Lake、52コアと独自巨大L3の全貌

- AMD 9950X3D2は899ドル、狙いはゲーマーではない

- Nova LakeはIPC優位、クロックはZen 6が制す

- Intel、LGA 1700にもう一度。5年目の延命とAMD戦略の本気度

- Ryzen 7 9800X3D、世界最安は日本という逆転現象

- AMD初の200W CPU、空冷では「性能を取りこぼす」とEKが警告

- CPU不足はメモリより深刻、Intel 18Aが命運を握る

- Ryzen 7 5800X3D、AM4 10周年で復活の噂